# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **General Description**

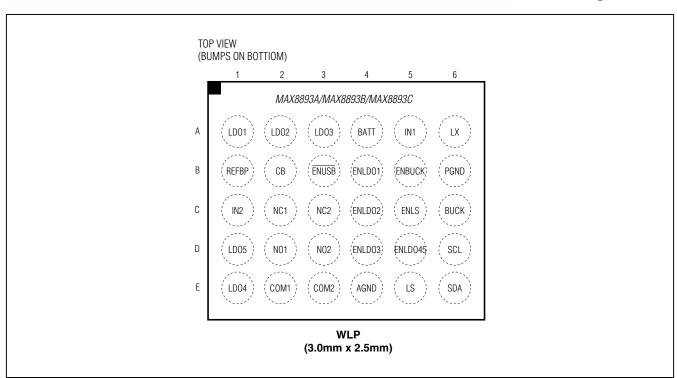

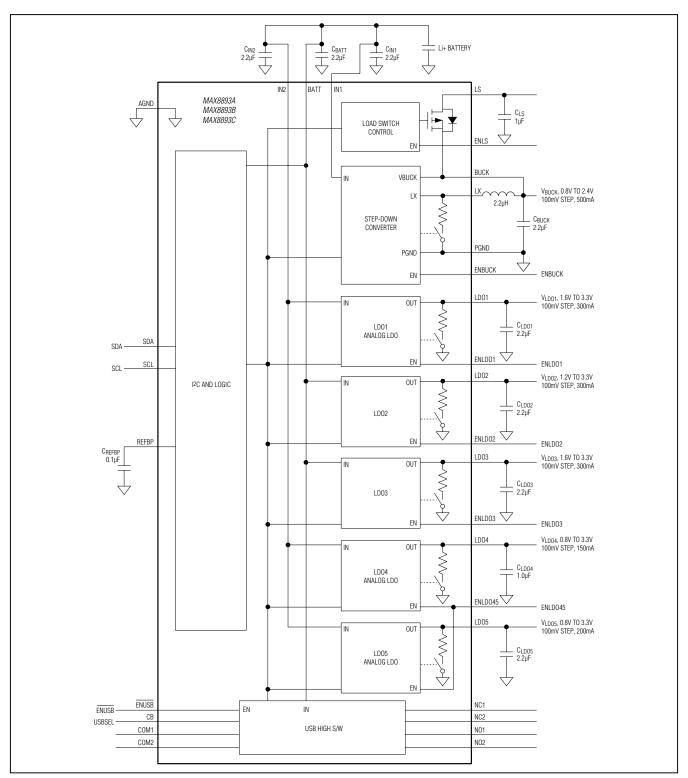

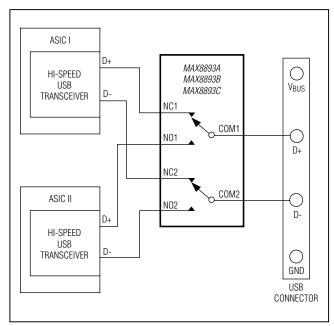

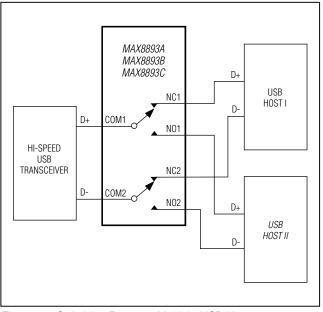

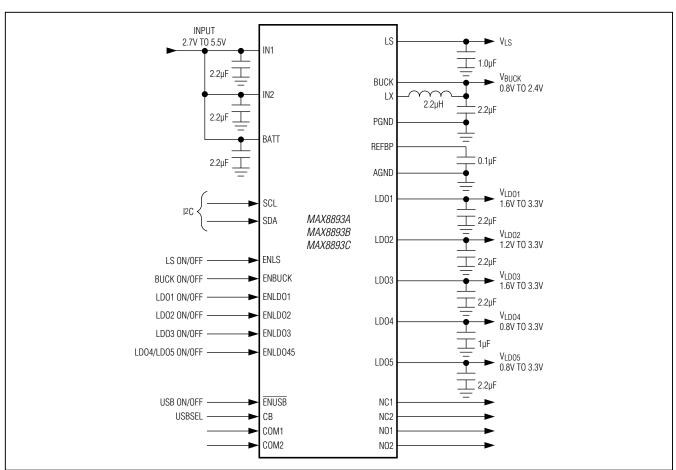

The MAX8893A/MAX8893B/MAX8893C power-management integrated circuits (PMICs) are designed for a variety of portable devices including cellular handsets. The PMICs include a high-efficiency step-down DC-DC converter, five low-dropout linear regulators (LDOs) with programmable output voltages, individual power-on/off control inputs, a load switch, and a USB high-speed switch. These devices maintain high efficiency with a low no-load supply current, and the small 3.0mm x 2.5mm WLP package makes them ideal for portable devices.

The step-down DC-DC converter utilizes a proprietary 4MHz hysteretic PWM control scheme that allows for ultra-small external components. Internal synchronous rectification improves efficiency and eliminates the external Schottky diode that is required in conventional step-down converters. Its output voltage is programmable by the I<sup>2</sup>C serial interface and output current is guaranteed up to 500mA.

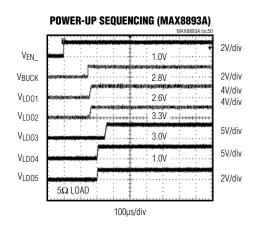

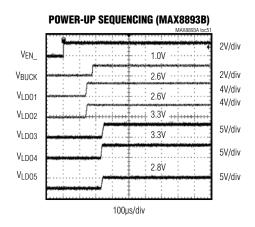

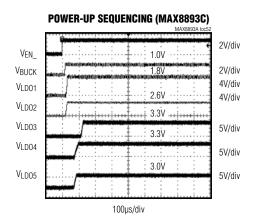

LDO1, LDO4, and LDO5 offer low 45µVRMS output noise and low dropout of only 100mV at 100mA. They deliver up to 300mA, 150mA, and 200mA continuous output currents, respectively. LDO2 and LDO3 each deliver 300mA continuous output current with very low ground current. All LDO output voltages are programmable by the I<sup>2</sup>C serial interface. Three standard versions of the PMIC are available with different LDO default startup voltages (see Table 1).

The MAX8893A/MAX8893B/MAX8893C are available in a 3.0mm  $\times$  2.5mm, 30-bump WLP package.

#### \_Applications

Cellular Handsets

Smartphones and PDAs

Typical Operating Circuit appears at end of data sheet.

Visit <u>www.maximintegrated.com/products/patents</u> for product patent marking information.

#### **Features**

- ♦ High-Efficiency Step-Down Converter Guaranteed 500mA Output Current Up to 4MHz Switching Frequency Programmable Output Voltage from 0.8V to 2.4V Dynamic Voltage Scaling with Programmable Ramp Rate

- ♦ Three Low-Noise LDOs with Programmable Output Voltages

- ♦ Two Low Supply Current LDOs with Programmable Output Voltages

- ♦ Low On-Resistance Load Switch

- ♦ USB High-Speed Switch with ±15kV ESD

- Individual Enable Control for All Regulators and Switches

- ♦ I<sup>2</sup>C Serial Interface

- ♦ Overcurrent and Thermal Protection for All LDOs

- ♦ 3.0mm x 2.5mm x 0.64mm, 30-Bump WLP

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE                    |

|--------------|----------------|--------------------------------|

| MAX8893AEWV+ | -40°C to +85°C | 30-Bump WLP<br>(3.0mm x 2.5mm) |

| MAX8893BEWV+ | -40°C to +85°C | 30-Bump WLP<br>(3.0mm x 2.5mm) |

| MAX8893CEWV+ | -40°C to +85°C | 30-Bump WLP<br>(3.0mm x 2.5mm) |

+Denotes a lead(Pb)-free/RoHS-compliant package.

# **μPMICs for Multimedia Application Processors** in a 3.0mm x 2.5mm WLP

#### **ABSOLUTE MAXIMUM RATINGS**

| IN1, IN2, BATT, COM1, COM2 to AGN | D0.3V to +6.0V                       |

|-----------------------------------|--------------------------------------|

| BUCK, LS, ENLS, ENBUCK, ENLDO1,   | ENLDO2,                              |

| ENLDO3, ENLDO45, REFBP, LDO2,     | LDO3,                                |

| SCL, SDA, ENUSB, CB, NC1, NC2,    |                                      |

| NO1, NO2 to AGND                  | $0.3V \text{ to } (V_{BATT} + 0.3V)$ |

| LDO1, LDO4, LDO5 to AGND          | 0.3V to $(V_{IN2} + 0.3V)$           |

| PGND to AGND                      | 0.3V to +0.3V                        |

| LX Current                        | 1.5ARMS                              |

| LX to AGND (Note 1)               | 0.3V to $(V_{IN1} + 0.3V)$           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>30-Bump, 3.0mm x 2.5mm WLP (derate 20.0 | •               |

|--------------------------------------------------------------------------------------------------|-----------------|

| above +70°C)                                                                                     |                 |

| Junction-to-Ambient Thermal Resistance (θJA)                                                     | )               |

| (Note 2)                                                                                         | 50°C/W          |

| Operating Temperature Range                                                                      | 40°C to +85°C   |

| Junction Temperature                                                                             |                 |

| Storage Temperature Range                                                                        | -65°C to +150°C |

| Bump Temperature (soldering)                                                                     |                 |

| Infrared (15s)                                                                                   | +200°C          |

| Vapor Phase (20s)                                                                                | +215°C          |

|                                                                                                  |                 |

- **Note 1:** LX has internal clap diodes to PGND and IN1. Applications that forward bias these diodes should take care not to exceed the IC's package-dissipation limits.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Typical Operating Circuit,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2\mu F$ ,  $C_{REFBP} = 0.1\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                          | CONDITIONS                                                                                    | MIN   | TYP   | MAX      | UNIT |

|------------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|----------|------|

| Input Supply Range                 |                                                                                               | 2.7   |       | 5.5      | V    |

| Shutdown Supply Current            | VCB = 0V or VIN, VENUSB = VIN, VENLS = VENBUCK = VENLDO1 = VENLDO2 = VENLDO3 = VENLDO45 = 0V  |       | 0.6   | 5        | μΑ   |

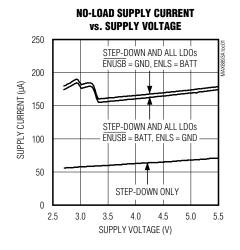

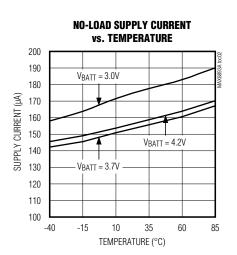

| No-Load Supply Current             | No load on BUCK, LDO1, LDO2, LDO3, LDO4, and LDO5, VENUSB = 0V, VENLS = VIN                   |       | 160   | 200      | μΑ   |

| Light-Load Supply Current          | BUCK on with 500µA load, all LDOs on with no load, VENUSB = 0V, VENLS = VIN                   |       | 315   |          | μΑ   |

| UNDERVOLTAGE LOCKOUT               |                                                                                               |       |       |          |      |

| Undervoltage Lockout (Note 5)      | V <sub>IN</sub> _rising                                                                       | 2.70  | 2.85  | 3.05     | V    |

| Officer voltage Lockout (Note 3)   | V <sub>IN</sub> _falling                                                                      |       | 2.35  | 2.55     | V    |

| THERMAL SHUTDOWN                   |                                                                                               |       |       |          |      |

| Thermal Shutdown Threshold         | T <sub>A</sub> rising                                                                         |       | 160   |          | °C   |

| Thermal Shutdown Hysteresis        |                                                                                               |       | 10    |          | °C   |

| REFERENCE                          |                                                                                               |       |       |          |      |

| Reference Bypass Output<br>Voltage |                                                                                               | 0.786 | 0.800 | 0.814    | V    |

| REF Supply Rejection               | $2.7V \le V_{IN} \le 5.5V$                                                                    |       | 0.2   |          | mV/V |

| LOGIC AND CONTROL INPUTS           |                                                                                               | ·     | ·     | <u> </u> | ·    |

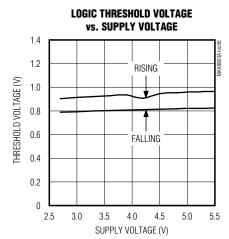

| Input Low Level                    | ENLS, ENBUCK, ENLDO1, ENLDO2, ENLDO3, ENLDO45, ENUSB, SDA, SCL, 2.7V ≤ V <sub>IN</sub> ≤ 5.5V |       |       | 0.4      | V    |

| Input High Level                   | ENLS, ENBUCK, ENLDO1, ENLDO2, ENLDO3, ENLDO45, ENUSB, SDA, SCL, 2.7V ≤ V <sub>IN</sub> ≤ 5.5V | 1.4   |       |          | V    |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Typical Operating Circuit,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2 \mu F$ ,  $C_{REFBP} = 0.1 \mu F$ ,  $T_{A} = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25 ^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                                                                      | CONDITION                                                              | IS                  |       | MIN   | TYP   | MAX   | UNIT |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|-------|-------|-------|-------|------|--|

| Lania lanat Ormana                                                             | CDA COL OV - VIII - F 5V                                               | T <sub>A</sub> = +2 | 5°C   | -1    |       | +1    |      |  |

| Logic Input Current                                                            | SDA, SCL, $0V < V_{IN} < 5.5V$ $T_A = +85^{\circ}C$                    |                     | 5°C   |       | 0.1   |       | μA   |  |

| ENUSB Pullup Resistor to BATT                                                  |                                                                        |                     |       | 400   | 800   | 1600  | kΩ   |  |

| ENLS, ENBUCK, ENLDO1,<br>ENLDO2, ENLDO3, ENLDO45,<br>Pulldown Resistor to AGND |                                                                        |                     |       | 400   | 800   | 1600  | kΩ   |  |

| STEP-DOWN DC-DC CONVERT                                                        | ER (BUCK)                                                              |                     |       |       |       |       |      |  |

| Supply Current                                                                 | I <sub>LOAD</sub> = 0A, no switching                                   |                     |       |       | 25    |       | μA   |  |

|                                                                                |                                                                        |                     |       | 0.776 | 0.800 | 0.824 |      |  |

|                                                                                |                                                                        |                     |       |       | 0.90  |       | ]    |  |

|                                                                                |                                                                        |                     |       | 0.97  | 1.00  | 1.03  |      |  |

|                                                                                |                                                                        |                     |       |       | 1.10  |       | 1    |  |

|                                                                                |                                                                        |                     |       |       | 1.20  |       |      |  |

|                                                                                |                                                                        |                     |       |       | 1.30  |       |      |  |

|                                                                                |                                                                        |                     |       |       | 1.40  |       |      |  |

|                                                                                | ILOAD = 100mA, programmable output voltage 0.8V to 2.4V in 100mV steps |                     |       |       | 1.50  |       |      |  |

| Programmable Output Voltage                                                    |                                                                        |                     | BV to |       | 1.60  |       | V    |  |

|                                                                                |                                                                        |                     |       |       | 1.70  |       | 1    |  |

|                                                                                |                                                                        |                     |       |       | 1.80  |       |      |  |

|                                                                                |                                                                        |                     |       |       | 1.90  |       | İ    |  |

|                                                                                |                                                                        |                     |       |       | 2.00  |       |      |  |

|                                                                                |                                                                        |                     |       |       | 2.10  |       |      |  |

|                                                                                |                                                                        |                     |       |       | 2.20  |       |      |  |

|                                                                                |                                                                        |                     |       | 2.231 | 2.300 | 2.369 | 1    |  |

|                                                                                |                                                                        |                     |       | 2.328 | 2.400 | 2.472 |      |  |

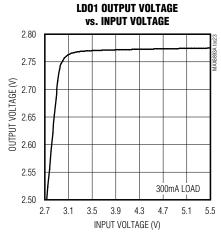

| Output-Voltage Line Regulation                                                 | VIN = 2.7V to 5.5V                                                     |                     |       |       | 0.3   |       | %/V  |  |

|                                                                                |                                                                        | $T_A = +2$          | 25°C  | -1    |       | +1    |      |  |

| LX Leakage Current                                                             | $V_{LX} = 0V \text{ or } 5.5V$                                         | $T_A = +8$          |       |       | 0.1   |       | μA   |  |

| 0                                                                              | p-MOSFET switch                                                        |                     |       | 600   | 990   | 1500  |      |  |

| Current Limit                                                                  | n-MOSFET rectifier                                                     |                     |       | 400   | 700   | 1300  | mA   |  |

| 0. 0. 1.1.                                                                     | p-MOSFET switch, I <sub>L</sub> X = -40mA                              |                     |       |       | 0.65  |       | _    |  |

| On-Resistance                                                                  | n-MOSFET rectifier, I <sub>L</sub> x = 40mA                            |                     |       |       | 0.4   |       | Ω    |  |

| Rectifier Off Current Threshold                                                | ILXOFF                                                                 |                     |       |       | 30    |       | mA   |  |

| Minimum On- and Off-Times                                                      | ton, toff                                                              |                     |       |       | 70    |       | ns   |  |

| Shutdown Output Resistance                                                     | BUCK_ADEN = 1, VENBUCK = 0V                                            |                     |       |       | 300   |       | Ω    |  |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2 \mu F$ ,  $C_{REFBP} = 0.1 \mu F$ ,  $T_A = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                                 | CONDITIONS                                                                                                       | MIN   | TYP   | MAX   | UNIT  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| LDO1                                      |                                                                                                                  | •     |       |       |       |

| Input Voltage Range                       |                                                                                                                  | 2.7   |       | 5.5   | V     |

|                                           |                                                                                                                  | 1.552 | 1.600 | 1.648 |       |

|                                           |                                                                                                                  |       | 1.70  |       | ]     |

|                                           |                                                                                                                  |       | 1.80  |       | ]     |

|                                           |                                                                                                                  |       | 1.90  |       |       |

|                                           |                                                                                                                  |       | 2.00  |       | ]     |

|                                           |                                                                                                                  |       | 2.10  |       |       |

|                                           |                                                                                                                  |       | 2.20  |       | ]     |

|                                           |                                                                                                                  |       | 2.30  |       |       |

| Dura sura sara a la la Ocata da Valta sur | I <sub>LOAD</sub> = 25mA, programmable output voltage 1.6V to                                                    |       | 2.40  |       | ] ,,  |

| Programmable Output Voltage               | 3.3V in 100mV steps                                                                                              |       | 2.50  |       | V     |

|                                           |                                                                                                                  |       | 2.60  |       | ]     |

|                                           |                                                                                                                  |       | 2.70  |       | 1     |

|                                           |                                                                                                                  |       | 2.80  |       | 1     |

|                                           |                                                                                                                  |       | 2.90  |       |       |

|                                           |                                                                                                                  | 2.910 | 3.000 | 3.090 |       |

|                                           |                                                                                                                  |       | 3.1   |       | 1     |

|                                           |                                                                                                                  |       | 3.2   | 1     |       |

|                                           |                                                                                                                  | 3.201 | 3.300 | 3.399 | 1     |

|                                           | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.2V$ with $I_{LOAD} = 300$ mA (MAX8893A)                  | 2.716 | 2.800 | 2.884 |       |

| Output Voltage Accuracy                   | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.0V$ with $I_{LOAD} = 300$ mA (MAX8893B)                  | 2.522 | 2.600 | 2.678 | V     |

|                                           | VIN = 5.5V with I <sub>LOAD</sub> = 1mA, and<br>V <sub>IN</sub> = 2.7V with I <sub>LOAD</sub> = 300mA (MAX8893C) | 1.746 | 1.800 | 1.854 | -     |

| Output Current                            |                                                                                                                  |       |       | 300   | mA    |

| Current Limit                             | VLDO1 = 0V                                                                                                       |       | 550   |       | mA    |

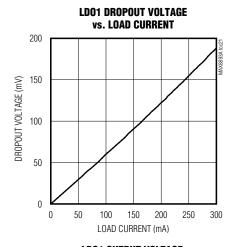

| Dropout Voltage                           | I <sub>LOAD</sub> = 200mA, T <sub>A</sub> = +25°C                                                                |       | 200   |       | mV    |

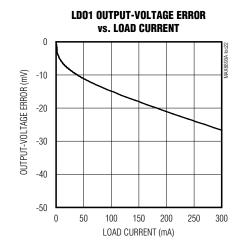

| Load Regulation                           | 1mA < I <sub>LOAD</sub> < 300mA<br>VENLDO1 = VBATT                                                               |       | 25    |       | mV    |

| Power-Supply Rejection<br>ΔVLDO1/ΔVIN2    | 10Hz to 10kHz, C <sub>LDO1</sub> = 1μF, I <sub>LOAD</sub> = 30mA                                                 |       | 75    |       | dB    |

| Output Noise Voltage                      | 100Hz to 100kHz, C <sub>LDO1</sub> = 1μF, I <sub>LOAD</sub> = 30mA                                               |       | 45    |       | μVRMS |

| Output Capacitor for Stable               | 0mA < I <sub>LOAD</sub> < 300mA                                                                                  | 1.4   | 2.2   |       |       |

| Operation (Note 6)                        | 0mA < ILOAD < 150mA                                                                                              | 0.7   | 1.0   |       | μF    |

| Ground Current                            | ILOAD = 500μA                                                                                                    |       | 21    |       | μΑ    |

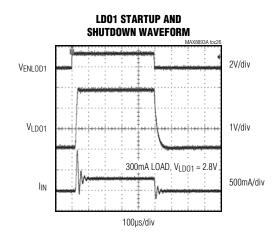

| Startup Time from Shutdown                | $C_{LDO1} = 2.2\mu F$ , $I_{LOAD} = 300 mA$                                                                      |       | 40    |       | μs    |

| Shutdown Output Resistance                | LDO1_ADEN = 1, VENLDO1 = 0V                                                                                      |       | 300   |       | Ω     |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2\mu F$ ,  $C_{REFBP} = 0.1\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                               | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| LDO2                                    |                                                                                      | •     |       |       | •     |  |

| Input Voltage Range                     |                                                                                      | 2.7   |       | 5.5   | V     |  |

|                                         |                                                                                      | 1.164 | 1.200 | 1.236 |       |  |

|                                         |                                                                                      |       | 1.30  |       | 1     |  |

|                                         |                                                                                      |       | 1.40  |       | 1     |  |

|                                         |                                                                                      |       | 1.50  |       | 1     |  |

|                                         |                                                                                      |       | 1.60  |       | 1     |  |

|                                         |                                                                                      |       | 1.70  |       | 1     |  |

|                                         |                                                                                      |       | 1.80  |       | 1     |  |

|                                         |                                                                                      |       | 1.90  |       | 1     |  |

|                                         |                                                                                      |       | 2.00  |       | 1     |  |

|                                         |                                                                                      |       | 2.10  |       | 1     |  |

|                                         | I <sub>LOAD</sub> = 25mA, programmable output voltage 1.2V to                        | 2.134 | 2.200 | 2.266 | 1 ,,  |  |

| Programmable Output Voltage             | 3.3V in 100mV steps                                                                  |       | 2.30  |       | V     |  |

|                                         |                                                                                      |       | 2.40  |       | 1     |  |

|                                         |                                                                                      |       | 2.50  |       | 1     |  |

|                                         |                                                                                      |       | 2.60  |       | 1     |  |

|                                         |                                                                                      |       | 2.70  |       | 1     |  |

|                                         |                                                                                      |       | 2.80  |       | 1     |  |

|                                         |                                                                                      |       | 2.90  |       | 1     |  |

|                                         |                                                                                      |       | 3.00  |       | 1     |  |

|                                         |                                                                                      |       | 3.10  |       | 1     |  |

|                                         |                                                                                      |       | 3.20  |       | 1     |  |

|                                         |                                                                                      | 3.201 | 3.300 | 3.399 | 1     |  |

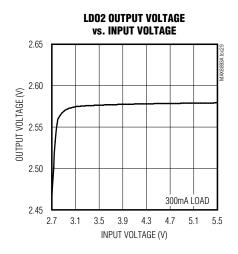

| Output Voltage Accuracy                 | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.0V$ with $I_{LOAD} = 300$ mA | 2.522 | 2.600 | 2.678 | V     |  |

| Output Current                          |                                                                                      |       |       | 300   | mA    |  |

| Current Limit                           | V <sub>LDO2</sub> = 0V                                                               |       | 550   |       | mA    |  |

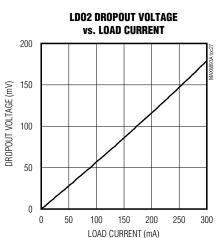

| Dropout Voltage                         | ILOAD = 200mA, TA = +25°C                                                            |       | 200   |       | mV    |  |

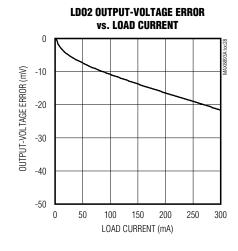

| Load Regulation                         | 1mA < ILOAD < 300mA<br>VENLDO2 = VBATT                                               |       | 25    |       | mV    |  |

| Power-Supply Rejection<br>ΔVLDO2/ΔVBATT | 10Hz to 10kHz, $C_{LDO2} = 1\mu F$ , $I_{LOAD} = 30mA$                               |       | 60    |       | dB    |  |

| Output Noise Voltage                    | 100Hz to 100kHz, C <sub>LDO2</sub> = 1µF, I <sub>LOAD</sub> = 30mA                   |       | 80    |       | μVRMS |  |

| Output Capacitor for Stable             | OmA < ILOAD < 300mA                                                                  | 1.4   | 2.2   |       |       |  |

| Operation (Note 6)                      | OmA < ILOAD < 150mA                                                                  | 0.7   | 1.0   |       | μF    |  |

| Ground Current                          | ILOAD = 500μA                                                                        |       | 21    |       | μΑ    |  |

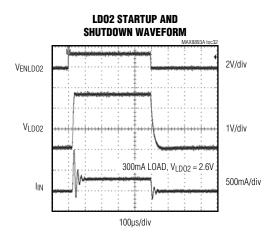

| Startup Time from Shutdown              | $C_{LDO2} = 1\mu F$ , $I_{LOAD} = 300 \text{mA}$                                     |       | 40    |       | μs    |  |

| Shutdown Output Resistance              | LDO2_ADEN = 1, VENLDO2 = 0V                                                          |       | 300   |       | Ω     |  |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2\mu F$ ,  $C_{REFBP} = 0.1\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                               | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT  |

|-----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|

| LDO3                                    |                                                                                      |       |       |       | ,     |

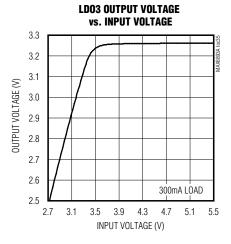

| Input Voltage Range                     |                                                                                      | 2.7   |       | 5.5   | V     |

|                                         |                                                                                      | 1.552 | 1.600 | 1.648 |       |

|                                         |                                                                                      |       | 1.70  |       | 1     |

|                                         |                                                                                      |       | 1.80  |       | 1     |

|                                         |                                                                                      |       | 1.90  |       | 1     |

|                                         |                                                                                      |       | 2.00  |       | 1     |

|                                         |                                                                                      |       | 2.10  |       | 1     |

|                                         |                                                                                      |       | 2.20  |       | 1     |

|                                         |                                                                                      |       | 2.30  |       |       |

|                                         | I <sub>LOAD</sub> = 25mA, programmable output voltage 1.6V to                        |       | 2.40  |       | 1 ,,  |

| Programmable Output Voltage             | 3.3V in 100mV steps                                                                  |       | 2.50  |       | \ \   |

|                                         |                                                                                      |       | 2.60  |       | 1     |

|                                         |                                                                                      |       | 2.70  |       | 1     |

|                                         |                                                                                      |       | 2.80  |       |       |

|                                         |                                                                                      |       | 2.90  |       |       |

|                                         |                                                                                      | 2.910 | 3.000 | 3.090 |       |

|                                         |                                                                                      |       | 3.10  |       |       |

|                                         |                                                                                      |       | 3.20  |       |       |

|                                         |                                                                                      | 3.201 | 3.300 | 3.399 |       |

| Output Voltage Accuracy                 | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.7V$ with $I_{LOAD} = 300$ mA | 3.201 | 3.300 | 3.399 | V     |

| Output Current                          |                                                                                      |       |       | 300   | mA    |

| Current Limit                           | V <sub>LDO3</sub> = 0V                                                               |       | 550   |       | mA    |

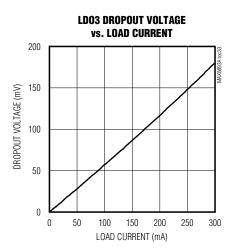

| Dropout Voltage                         | ILOAD = 200mA, TA = +25°C                                                            |       | 200   |       | mV    |

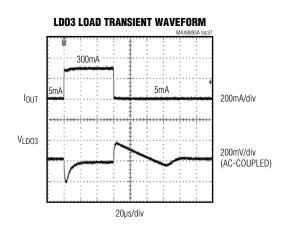

| Load Regulation                         | 1mA < ILOAD < 300mA<br>VENLDO3 = VBATT                                               |       | 25    |       | mV    |

| Power-Supply Rejection<br>ΔVLDO3/ΔVBATT | 10Hz to 10kHz, CLDO3 = $1\mu$ F, ILOAD = $30$ mA                                     |       | 60    |       | dB    |

| Output Noise Voltage                    | 100Hz to 100kHz, C <sub>LDO3</sub> = 1µF, I <sub>LOAD</sub> = 30mA                   |       | 80    |       | μVRMS |

| Output Capacitor for Stable             | 0mA < ILOAD < 300mA                                                                  | 1.4   | 2.2   |       | μF    |

| Operation (Note 6)                      | 0mA < I <sub>LOAD</sub> < 150mA                                                      | 0.7   | 1.0   |       |       |

| Ground Current                          | I <sub>LOAD</sub> = 500μA                                                            |       | 21    |       | μΑ    |

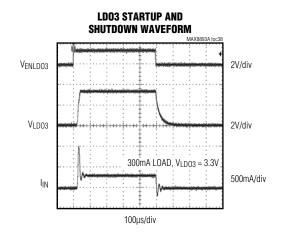

| Startup Time from Shutdown              | C <sub>LDO3</sub> = 2.2µF, I <sub>LOAD</sub> = 300mA                                 |       | 40    |       | μs    |

| Shutdown Output Resistance              | LDO3_ADEN = 1, VENLDO3 = 0V                                                          |       | 300   |       | Ω     |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2\mu F$ ,  $C_{REFBP} = 0.1\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 3, 4)

| LDO4                                   |                                                                                                          |       |       |       |          |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|--|--|--|

| Input Voltage Range                    |                                                                                                          | 2.7   |       | 5.5   | V        |  |  |  |

|                                        |                                                                                                          | 0.776 | 0.800 | 0.824 | 4        |  |  |  |

|                                        |                                                                                                          |       | 0.90  |       | ]        |  |  |  |

|                                        |                                                                                                          |       | 1.00  |       |          |  |  |  |

|                                        |                                                                                                          |       | 1.10  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 1.20  |       | -        |  |  |  |

|                                        |                                                                                                          |       | 1.30  |       | ]        |  |  |  |

|                                        |                                                                                                          | 1.358 | 1.400 | 1.442 | -        |  |  |  |

|                                        |                                                                                                          |       | 1.50  |       | ]        |  |  |  |

|                                        |                                                                                                          |       | 1.60  |       | -        |  |  |  |

|                                        |                                                                                                          |       | 1.70  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 1.80  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 1.90  |       | 1        |  |  |  |

|                                        | ILOAD = 25mA, programmable output voltage 0.8V to                                                        |       | 2.00  |       |          |  |  |  |

| Programmable Output Voltage            | 3.3V in 100mV steps                                                                                      |       | 2.10  |       | - V      |  |  |  |

|                                        | '                                                                                                        |       | 2.20  |       |          |  |  |  |

|                                        |                                                                                                          |       | 2.30  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 2.40  |       |          |  |  |  |

|                                        |                                                                                                          |       | 2.50  |       |          |  |  |  |

|                                        |                                                                                                          |       | 2.60  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 2.70  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 2.80  |       | 1        |  |  |  |

|                                        |                                                                                                          |       | 2.90  |       | $\dashv$ |  |  |  |

|                                        |                                                                                                          |       | 3.00  |       |          |  |  |  |

|                                        |                                                                                                          |       | 3.10  |       |          |  |  |  |

|                                        |                                                                                                          |       | 3.20  |       |          |  |  |  |

|                                        |                                                                                                          | 3.201 | 3.300 | 3.399 | -        |  |  |  |

|                                        | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.4V$ with $I_{LOAD} = 150$ mA (MAX8893A)          | 2.910 | 3.000 | 3.090 | .,       |  |  |  |

| Output Voltage Accuracy                | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.7V$ with $I_{LOAD} = 150$ mA (MAX8893B/MAX8893C) | 3.201 | 3.300 | 3.399 | V        |  |  |  |

| Output Current                         |                                                                                                          |       |       | 150   | mA       |  |  |  |

| Current Limit                          | V <sub>LDO4</sub> = 0V                                                                                   |       | 360   |       | mA       |  |  |  |

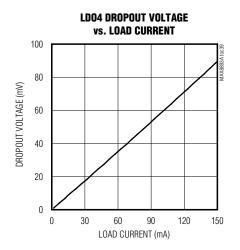

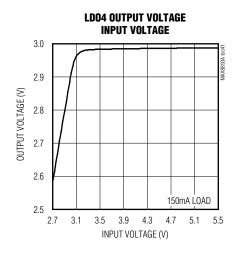

| Dropout Voltage                        | I <sub>LOAD</sub> = 100mA                                                                                |       | 100   |       | mV       |  |  |  |

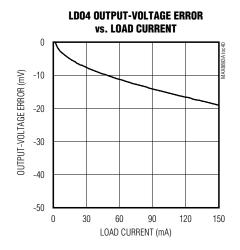

| Load Regulation                        | 1mA < I <sub>LOAD</sub> < 150mA, V <sub>ENLDO4</sub> = V <sub>BATT</sub>                                 |       | 25    |       | mV       |  |  |  |

| Power-Supply Rejection<br>ΔVLDO4/ΔVIN2 | 10Hz to 10kHz, C <sub>LDO4</sub> = 1µF, I <sub>LOAD</sub> = 30mA                                         |       | 75    |       | dB       |  |  |  |

| Output Noise Voltage                   | 100Hz to 100kHz, C <sub>LDO4</sub> = 1μF, I <sub>LOAD</sub> = 30mA                                       |       | 45    |       | μVRMS    |  |  |  |

| Output Capacitor for Stable Operation  | 0mA < ILOAD < 150mA (Note 6)                                                                             | 0.7   | 1.0   |       | μF       |  |  |  |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2 \mu F$ ,  $C_{REFBP} = 0.1 \mu F$ ,  $T_{A} = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25 ^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                   | CONDITIONS                                                                                      | MIN   | TYP   | MAX   | UNIT |

|-----------------------------|-------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Ground Current              | ILOAD = 500μA                                                                                   |       | 21    |       | μΑ   |

| Startup Time from Shutdown  | $CLDO4 = 1.0\mu F$ , $ILOAD = 150mA$                                                            |       | 40    |       | μs   |

| Shutdown Output Resistance  | LDO4_ADEN = 1, V <sub>ENLDO4</sub> = 0V                                                         |       | 300   |       | Ω    |

| LDO5                        |                                                                                                 |       | ,     |       |      |

| Input Voltage Range         |                                                                                                 | 2.7   |       | 5.5   | V    |

|                             |                                                                                                 | 0.776 | 0.800 | 0.824 |      |

|                             |                                                                                                 |       | 0.90  |       |      |

|                             |                                                                                                 |       | 1.00  |       |      |

|                             |                                                                                                 |       | 1.10  |       |      |

|                             |                                                                                                 |       | 1.20  |       |      |

|                             |                                                                                                 |       | 1.30  |       |      |

|                             |                                                                                                 | 1.358 | 1.400 | 1.442 |      |

|                             |                                                                                                 |       | 1.50  |       |      |

|                             |                                                                                                 |       | 1.60  |       |      |

|                             |                                                                                                 |       | 1.70  |       |      |

|                             |                                                                                                 |       | 1.80  |       |      |

|                             |                                                                                                 |       | 1.90  |       |      |

| Programmable Output Voltage | ILOAD = 100mA, programmable output voltage 0.8V to                                              |       | 2.00  | V     |      |

| Trogrammable Output Voltage | 3.3V in 100mV steps                                                                             |       | 2.10  | _ `   |      |

|                             |                                                                                                 |       | 2.20  |       |      |

|                             |                                                                                                 |       | 2.30  |       |      |

|                             |                                                                                                 |       | 2.40  |       |      |

|                             |                                                                                                 |       | 2.50  |       |      |

|                             |                                                                                                 |       | 2.60  |       |      |

|                             |                                                                                                 |       | 2.70  |       |      |

|                             |                                                                                                 |       | 2.80  |       |      |

|                             |                                                                                                 |       | 2.90  |       |      |

|                             |                                                                                                 |       | 3.00  |       |      |

|                             |                                                                                                 |       | 3.10  |       |      |

|                             |                                                                                                 |       | 3.20  |       |      |

|                             |                                                                                                 | 3.201 | 3.300 | 3.399 |      |

|                             | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.4V$ with $I_{LOAD} = 150$ mA (MAX8893A) | 0.970 | 1.000 | 1.030 |      |

| Output Voltage Accuracy     | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.4V$ with $I_{LOAD} = 150$ mA (MAX8893B) | 2.716 | 2.800 | 2.884 | V    |

|                             | $V_{IN} = 5.5V$ with $I_{LOAD} = 1$ mA, and $V_{IN} = 3.4V$ with $I_{LOAD} = 150$ mA (MAX8893C) | 2.910 | 3.000 | 3.090 |      |

| Output Current              |                                                                                                 |       |       | 200   | mA   |

| Current Limit               | V <sub>LDO5</sub> = 0V                                                                          |       | 460   |       | mA   |

| Dropout Voltage             | ILOAD = 100mA                                                                                   |       | 100   |       | mV   |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Typical Operating Circuit,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2 \mu F$ ,  $C_{REFBP} = 0.1 \mu F$ ,  $T_{A} = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25 ^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                                                | CONDITIONS                                                             |                          | MIN                   | TYP                   | MAX                   | UNIT  |  |

|----------------------------------------------------------|------------------------------------------------------------------------|--------------------------|-----------------------|-----------------------|-----------------------|-------|--|

| Load Regulation                                          | 1mA < I <sub>LOAD</sub> < 150mA<br>VENLDO5 = VBATT                     |                          |                       | 25                    |                       | mV    |  |

| Power-Supply Rejection<br>ΔVLDO5/ΔVIN2                   | 10Hz to 10kHz, C <sub>LDO5</sub> = 1µF, I <sub>LOAD</sub> :            | = 30mA                   |                       | 75                    |                       | dB    |  |

| Output Noise Voltage                                     | 100Hz to 100kHz, CLDO5 = 1µF, ILOA                                     | D = 30mA                 |                       | 45                    |                       | μVRMS |  |

| Output Capacitor for Stable                              | 0mA < I <sub>LOAD</sub> < 200mA                                        |                          | 1.4                   | 2.2                   |                       | μF    |  |

| Operation (Note 6)                                       | 0mA < ILOAD < 150mA                                                    |                          | 0.7                   | 1.0                   |                       | μΓ    |  |

| Ground Current                                           | I <sub>LOAD</sub> = 500μA                                              |                          |                       | 21                    |                       | μA    |  |

| Startup Time from Shutdown                               | $C_{LDO5} = 2.2 \mu F$ , $I_{LOAD} = 200 mA$                           |                          |                       | 40                    |                       | μs    |  |

| Shutdown Output Resistance                               | LDO5_ADEN = 1, V <sub>ENLDO5</sub> = 0V                                |                          |                       | 300                   |                       | Ω     |  |

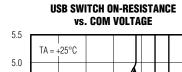

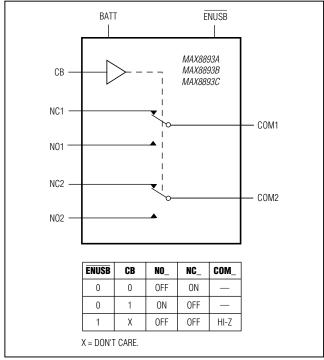

| USB HIGH-SPEED SWITCH                                    |                                                                        |                          | ,                     |                       |                       |       |  |

| Operating Power-Supply Range                             |                                                                        |                          | 2.7                   |                       | 5.5                   | V     |  |

| Supply Current                                           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                 | VBATT = 3.0V             |                       | 0.6                   |                       |       |  |

| Supply Current                                           | VENUSB = 0V, VCB = 0V or VBATT                                         | V <sub>BATT</sub> = 5.5V |                       | 3                     |                       | μΑ    |  |

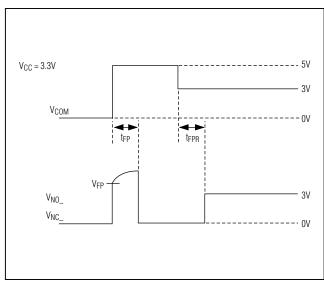

| Fault Protection Trip Threshold (VFP)                    | COM_ only, T <sub>A</sub> = +25°C                                      |                          | V <sub>IN</sub> + 0.6 | V <sub>IN</sub> + 0.8 | V <sub>IN</sub> + 1.0 | ٧     |  |

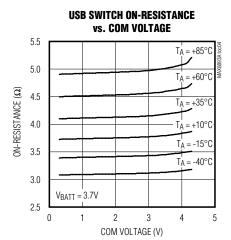

| 0. 5                                                     | V <sub>COM</sub> = 0V to V <sub>BATT</sub>                             |                          |                       | 5                     | 10                    |       |  |

| On-Resistance (R <sub>ON</sub> )                         | V <sub>COM</sub> = 3.6V, V <sub>BATT</sub> = 3.0V                      |                          |                       | 5.5                   |                       | Ω     |  |

| On-Resistance Match Between Channels ( $\Delta R_{ON}$ ) | V <sub>BATT</sub> = 3.0V, V <sub>COM</sub> = 2V (Note 7)               |                          |                       | 0.1                   | 1                     | Ω     |  |

| On-Resistance Flatness (RFLAT)                           | VBATT = 3.0V, VCOM_ = 0V to VIN (No                                    | te 8)                    |                       | 0.1                   |                       | Ω     |  |

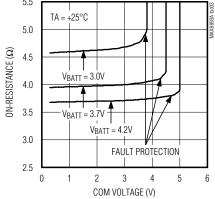

| Off-Leakage Current                                      | VBATT = 4.5V, VCOM_ = 0V or 4.5V,<br>VNO_, VNC_ = 4.5V or 0V           |                          | -250                  |                       | +250                  | nA    |  |

| (ICOM_(OFF))                                             | VBATT = 5.5V, VCOM_ = 0V or 5.5V, VNO_, VNC_ with 50µA sink current to | AGND                     |                       |                       | 180                   | μA    |  |

| On-Leakage Current (ICOM_(ON))                           | VBATT = 5.5V, VCOM_ = 0V or 5.5V, VNO_, and VNC_ are unconnected       |                          | -250                  |                       | +250                  | nA    |  |

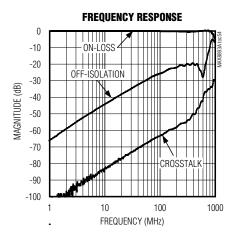

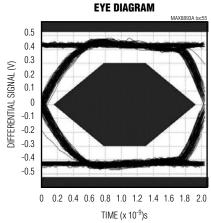

| <b>USB HIGH-SPEED SWITCH AC F</b>                        | PERFORMANCE                                                            |                          | '                     |                       |                       |       |  |

| On-Channel -3dB Bandwidth (BW)                           | $R_L = R_S = 50\Omega$ , signal = 0dBm                                 |                          |                       | 950                   |                       | MHz   |  |

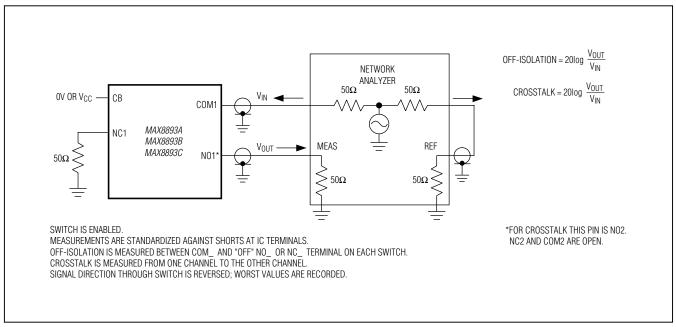

|                                                          | V <sub>NO_</sub> , V <sub>NC_</sub> = 0dBm,                            | f = 10MHz                |                       | -48                   |                       |       |  |

| Off-Isolation (VISO)                                     | $R_L = R_S = 50\Omega$ ,                                               | f = 250MHz               |                       | -20                   |                       | dB    |  |

| ( 1.55)                                                  | Figure 1                                                               | f = 500MHz               |                       | -17                   |                       |       |  |

|                                                          | V <sub>NO_</sub> , V <sub>NC_</sub> = 0dBm,                            | f = 10MHz                |                       | -73                   |                       |       |  |

| Crosstalk (V <sub>CT</sub> )                             | $R_L = R_S = 50\Omega$ ,                                               | f = 250MHz               |                       | -54                   |                       | dB    |  |

| , - ,                                                    | Figure 1 (Note 9)                                                      | f = 500MHz               |                       | -33                   |                       |       |  |

| USB HIGH-SPEED SWITCH LOG                                | GIC INPUT (CB)                                                         | -L.                      | 1                     |                       |                       | 1     |  |

| Input Logic-High (VIH)                                   |                                                                        |                          | 1.4                   |                       |                       | V     |  |

| Input Logic-Low (VIL)                                    |                                                                        |                          |                       |                       | 0.4                   | V     |  |

| Input Leakage Current (I <sub>IN</sub> )                 |                                                                        |                          | -250                  |                       | +250                  | nA    |  |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Operating Circuit*,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2\mu F$ ,  $C_{REFBP} = 0.1\mu F$ ,  $T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                                            | CONDITIONS                                                                                                  | MIN | TYP  | MAX | UNIT |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| USB HIGH-SPEED SWITCH DYN                            | NAMIC                                                                                                       |     | ,    |     |      |

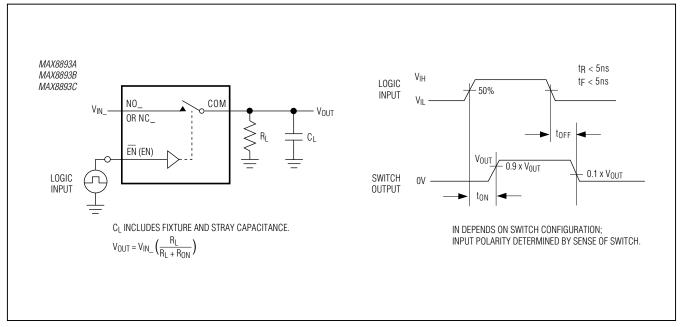

| Turn-On Time (ton)                                   | $V_{NO}$ or $V_{NC}$ = 1.5V, $R_L$ = 300 $\Omega$ , $C_L$ = 35pF, $V_{ENUSB}$ = $V_{BATT}$ to 0V, Figure 2  |     | 1    | 5   | μs   |

| Turn-Off Time (toff)                                 | $V_{NO}$ or $V_{NC}$ = 1.5V, $R_L$ = 300 $\Omega$ , $C_L$ = 35pF, $V_{ENUSB}$ = 0V to $V_{BATT}$ , Figure 2 |     | 1    | 5   | μs   |

| Propagation Delay (tPLH, tPHL)                       | $R_L = R_S = 50\Omega$ , Figure 3                                                                           |     | 100  |     | ps   |

| Fault Protection Response Time (tpp)                 | $V_{COM}$ = 0V to 5V step, $R_L$ = $R_S$ = $50\Omega$ , $V_{BATT}$ = 3.3V, Figure 4                         | 0.5 |      | 5.0 | μs   |

| Fault Protection Recovery Time (tppR)                | $V_{COM}$ = 5V to 0V step, $R_L$ = $R_S$ = $50\Omega$ , $V_{BATT}$ = 3.3V, Figure 4                         |     |      | 100 | μs   |

| Output Skew Between Switches (tsk)                   | Skew between switch 1 and 2, $R_L = R_S = 50\Omega$ , Figure 3 (Note 6)                                     |     | 40   |     | ps   |

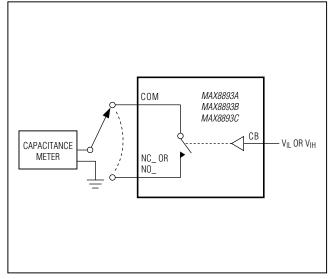

| NO_ or NC_ Off-Capacitance<br>(CNO(OFF) or CNC(OFF)) | f = 1MHz, Figure 5 (Note 6)                                                                                 |     | 2    |     | pF   |

| COM Off-Capacitance                                  | f = 1MHz, Figure 5                                                                                          |     | 5.5  |     | pF   |

| (CCOM(OFF)) (Note 6)                                 | f = 240 MHz, Figure 5                                                                                       |     | 4.8  |     | PI   |

| COM On-Capacitance                                   | f = 1MHz, Figure 5                                                                                          |     | 6.5  |     | pF   |

| (C <sub>COM(ON)</sub> ) (Note 6)                     | f = 240 MHz, Figure 5                                                                                       |     | 5.5  |     | Pi   |

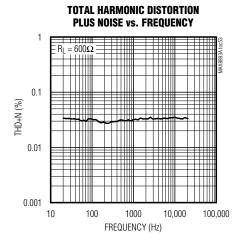

| Total Harmonic Distortion Plus<br>Noise              | $V_{COM}$ = 1 $V_{P-P}$ , $V_{BIAS}$ = 1 $V$ , $R_L$ = $R_S$ = 50 $\Omega$ , $f$ = 20 $Hz$ to 20 $Hz$       |     | 0.03 |     | %    |

| USB HIGH-SPEED SWITCH—ES                             | D PROTECTION                                                                                                |     |      |     |      |

| ENUSB, CB, NC1, NC2, NO1, NO2                        | Human Body Model                                                                                            |     | ±2   |     | kV   |

|                                                      | Human Body Model                                                                                            |     | ±15  |     |      |

| COM1, COM2                                           | IEC 61000-4-2 Air-Gap Discharge                                                                             |     | ±15  |     | kV   |

|                                                      | IEC 61000-4-2 Contact Discharge                                                                             |     | ±8   |     | 1    |

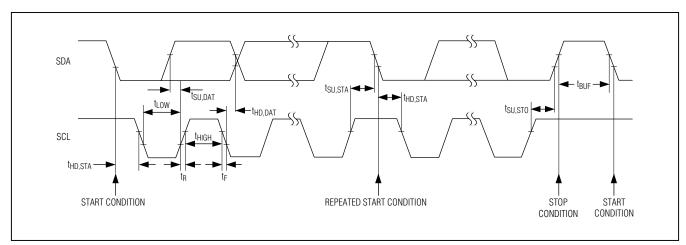

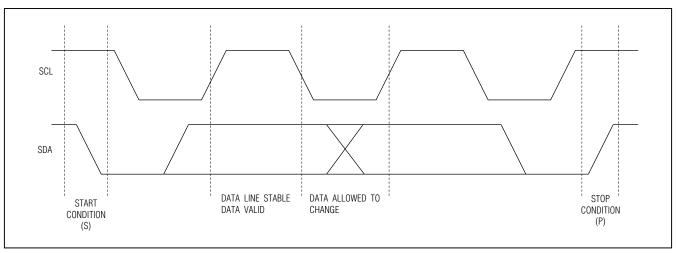

| I <sup>2</sup> C SERIAL INTERFACE (Figure            | 8)                                                                                                          |     |      |     |      |

| Clock Frequency                                      |                                                                                                             |     |      | 400 | kHz  |

| Bus-Free Time Between START and STOP (tBUF)          |                                                                                                             | 1.3 |      |     | μs   |

| Hold Time Repeated START Condition (tHD_STA)         |                                                                                                             | 0.6 |      |     | μs   |

| SCL Low Period (tLOW)                                |                                                                                                             | 1.3 |      |     | μs   |

| SCL High Period (tHIGH)                              |                                                                                                             | 0.6 |      |     | μs   |

| Setup Time Repeated START Condition (tsu_sta)        |                                                                                                             | 0.6 |      |     | μs   |

| SDA Hold Time (tHD_DAT)                              |                                                                                                             | 0   |      |     | μs   |

| SDA Setup time (t <sub>SU_DAT</sub> )                |                                                                                                             | 100 |      |     | ns   |

| Setup Time for STOP Condition (tsu_sto)              |                                                                                                             | 0.6 |      |     | μs   |

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Typical Operating Circuit,  $V_{IN} = 3.7V$ ,  $C_{BATT} = C_{IN1} = C_{IN2} = 2.2 \mu F$ ,  $C_{REFBP} = 0.1 \mu F$ ,  $T_{A} = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25 ^{\circ}C$ .) (Notes 3, 4)

| PARAMETER                                | CONDITIONS                                                                                 |                                 |     | TYP  | MAX | UNIT |  |

|------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------|-----|------|-----|------|--|

| Maximum Pulse Width of Spikes Suppressed |                                                                                            |                                 |     | 50   |     | ns   |  |

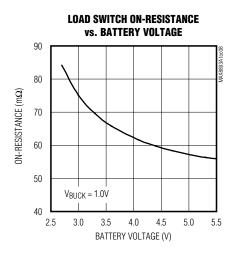

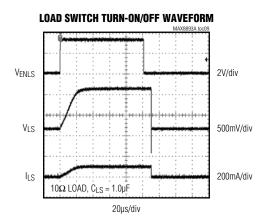

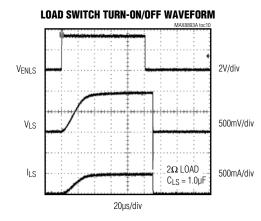

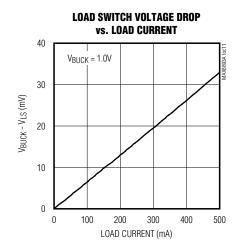

| LOAD SWITCH (LS)                         |                                                                                            |                                 |     |      |     |      |  |

| Input Supply Operating Range (VBUCK)     | After VBUCK starts up                                                                      |                                 | 0.8 |      | 2.4 | V    |  |

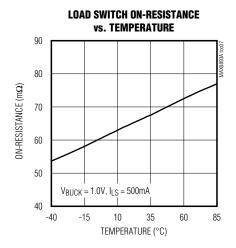

| On-Resistance (RDS(ON))                  | VBUCK = 1.0V, ILS = 300mA, TA = +                                                          | 25°C                            |     | 50   | 100 | mΩ   |  |

|                                          | VI 0 0 4V Di 4000 VEVI 0                                                                   | C <sub>L</sub> = 0.1µF          |     | 0.85 |     |      |  |

|                                          | $V_{LS} = 2.4V$ , $R_{L} = 400\Omega$ , $V_{ENLS} = 1.8V$ , Register LSTOD = 0 (Note 6)    | $C_L = 1\mu F$                  |     | 0.85 |     |      |  |

| Turn-On Delay Time (ton_dLy)             | 1.0V, Hegister EUTOD = 0 (Note 0)                                                          | C <sub>L</sub> = 3µF            |     | 0.85 |     | μs   |  |

| Turn-On Delay Time (ton_DLY)             | $V_{LS} = 2.4V$ , $R_{L} = 400\Omega$ , $V_{ENLS} =$                                       | $C_L = 0.1 \mu F$               |     | 30   |     | μδ   |  |

|                                          | 1.8V, Register LSTOD = 1                                                                   | $C_L = 1\mu F$                  |     | 34   |     |      |  |

|                                          | 1.0V, Hegister Lorob = 1                                                                   | C <sub>L</sub> = 3µF            |     | 37   |     |      |  |

|                                          | Vi o 2 4V Di 4000 VEVI o                                                                   | $C_L = 0.1 \mu F$               |     | 10   |     |      |  |

|                                          | $V_{LS} = 2.4V$ , $R_{L} = 400\Omega$ , $V_{ENLS} = 1.8V$ , Register LSRT = 0              | $C_L = 1\mu F \text{ (Note 6)}$ |     | 10   |     |      |  |

|                                          | 1.0V, Hegister Lotti = 0                                                                   | $C_L = 3\mu F \text{ (Note 6)}$ |     | 10   |     |      |  |

|                                          | V <sub>LS</sub> = 2.4V, R <sub>L</sub> = 400Ω, V <sub>ENLS</sub> = 1.8V, Register LSRT = 1 | $C_L = 0.1 \mu F$               |     | 25   |     |      |  |

|                                          |                                                                                            | $C_L = 1\mu F$                  |     | 27   |     |      |  |

| LS Rise Time (t <sub>R</sub> )           | 1.0V, Hegister Lotti = 1                                                                   | CL = 3µF                        |     | 30   |     |      |  |

|                                          | Vi a 2 4V Di 4000 V/Ti ii a                                                                | $C_L = 0.1 \mu F$               |     | 100  |     | μs   |  |

|                                          | $V_{LS} = 2.4V$ , $R_{L} = 400\Omega$ , $V_{ENLS} = 1.8V$ , Register LSRT = 2              | $C_L = 1\mu F$                  |     | 100  |     |      |  |

|                                          | 1.0V, Hegister Lotti = 2                                                                   | C <sub>L</sub> = 3µF            |     | 100  |     |      |  |

|                                          | Vi a 0 4V/ Di 4000 V/Ti ii a                                                               | $C_L = 0.1 \mu F$               |     | 300  |     |      |  |

|                                          | $V_{LS} = 2.4V$ , $R_{L} = 400\Omega$ , $V_{ENLS} = 1.8V$ , Register LSRT = 3              | $C_L = 1\mu F$                  |     | 300  |     |      |  |

|                                          | 1.0V, Hegister Lotti = 0                                                                   | C <sub>L</sub> = 3µF            |     | 300  |     |      |  |

|                                          | Vi a 2 4V Di 4000 V/Ti i a                                                                 | $C_L = 0.1 \mu F$               |     | 11   |     |      |  |

| Turn-Off Delay Time (tOFF_DLY)           | $V_{LS} = 2.4V, R_{L} = 400\Omega, V_{ENLS} = 1.8V$                                        | $C_L = 1\mu F$                  |     | 11   |     | μs   |  |

|                                          | 1.00                                                                                       | C <sub>L</sub> = 3µF            |     | 11   |     |      |  |

|                                          | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                     | C <sub>L</sub> = 0.1µF          |     | 15   |     |      |  |

| LS Fall Time (t <sub>F</sub> )           | $V_{LS} = 2.4V, R_{L} = 400\Omega, V_{ENLS} = 1.8V$                                        | $C_L = 1\mu F$                  |     | 150  |     | μs   |  |

|                                          | $C_L = 3\mu F$                                                                             |                                 |     | 447  |     |      |  |

| Shutdown Output Resistance               | V <sub>LS</sub> = 2.4V, V <sub>ENLS</sub> = 0V, LS_ADEN =                                  |                                 | 100 | 200  | Ω   |      |  |

- Note 3: V<sub>IN1</sub>, V<sub>IN2</sub>, and V<sub>BATT</sub> are connected together and single input is referred to as V<sub>IN</sub>.

- **Note 4:** All units are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

- **Note 5:** When the input voltage is greater than 2.85V (typ), the UVLO comparator trips, and the threshold is reduced to 2.35V (typ). This allows the system to start normally even if the input voltage decays to 2.35V.

- Note 6: Not production tested; guaranteed by design.

- Note 7:  $\Delta Ron(MAX) = IRon(CH1) Ron(CH2)I$ .

- **Note 8:** Flatness is defined as the difference between the maximum and minimum value of on-resistance, as measured over specified analog signal ranges.

- Note 9: Between any two switches.

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

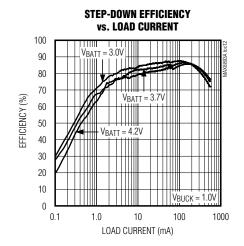

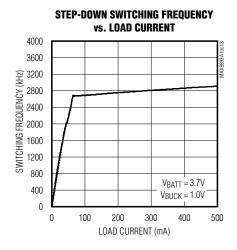

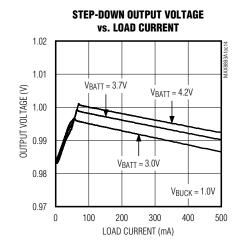

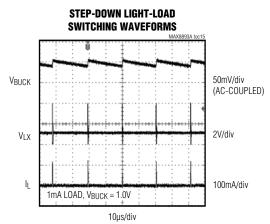

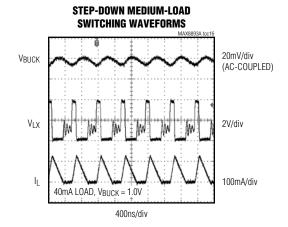

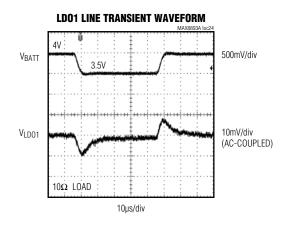

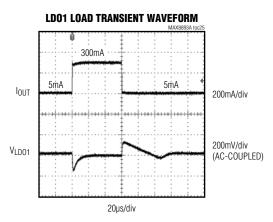

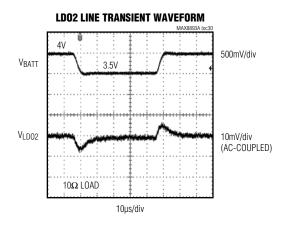

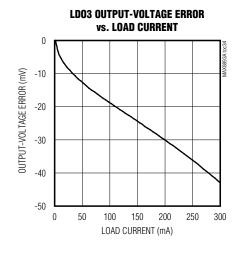

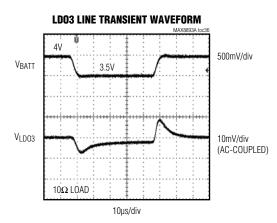

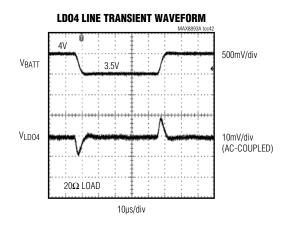

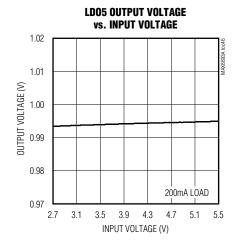

### **Typical Operating Characteristics**

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

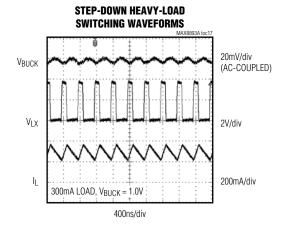

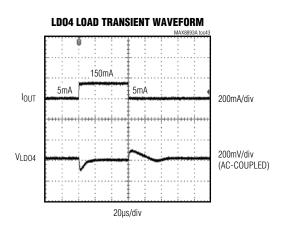

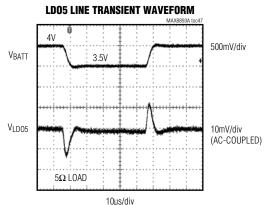

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

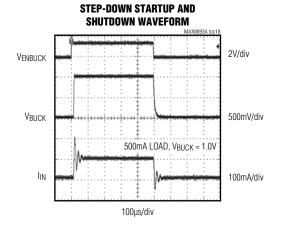

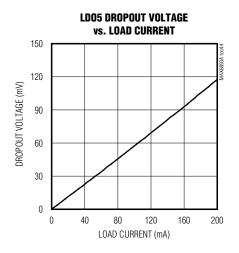

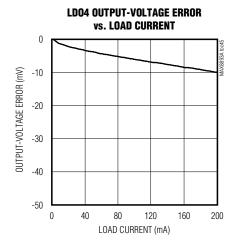

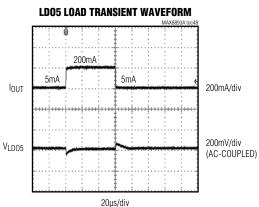

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

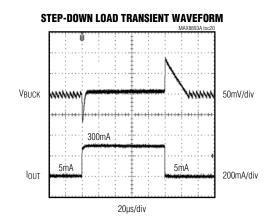

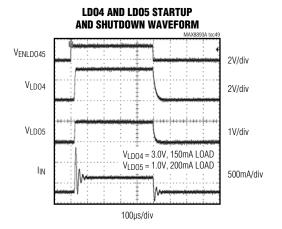

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2μF, C<sub>REFBP</sub> = 0.1μF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# VBATTI 4V 0 3.5V 500mV/div VBUCK 20mA/div (AC-COUPLED) 10Ω LOAD 10μs/div

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2μF, C<sub>REFBP</sub> = 0.1μF, T<sub>A</sub> = +25°C, unless otherwise noted.)

###

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### **Typical Operating Characteristics (continued)**

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

#### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN</sub> = 3.7V, C<sub>BATT</sub> = C<sub>IN1</sub> = C<sub>IN2</sub> = 2.2µF, C<sub>REFBP</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# μPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP

### **Test Circuits/Timing Diagrams**

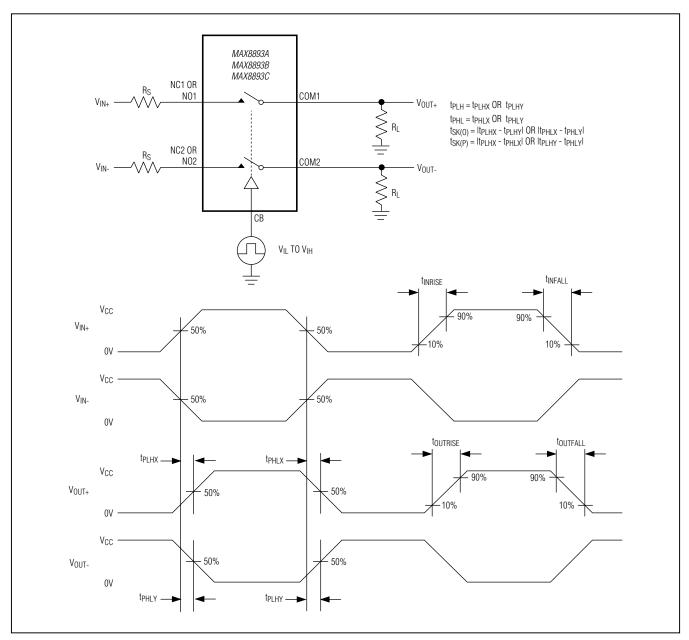

Figure 1. USB High-Speed Switch Off-Isolation and Crosstalk

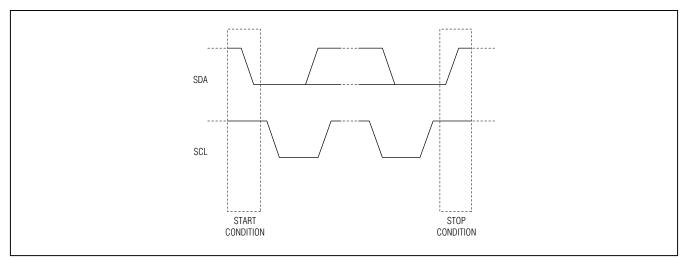

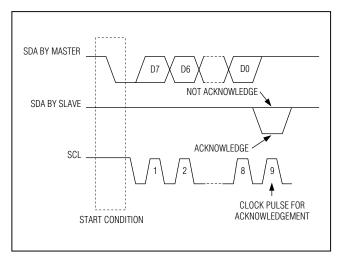

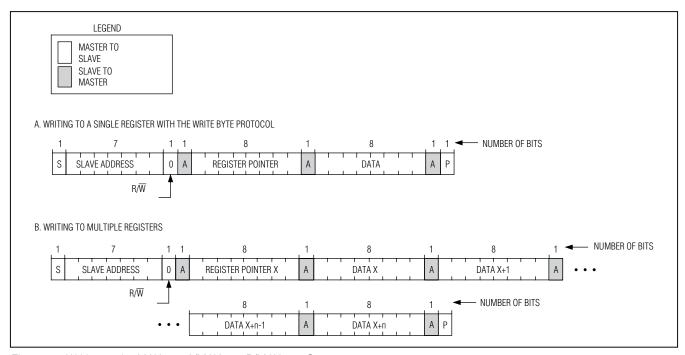

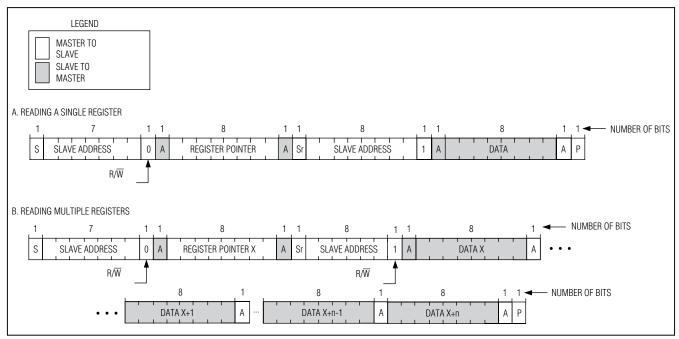

Figure 2. USB High-Speed Switch Switching Time