Merancang Penjana Pulse Tunggal untuk FPGA: Menyegerakkan Lebar dan Fasa Pulse

2024-12-17

5111

Katalog

Pengenalan

Dalam bidang pembangunan FPGA, mencipta denyutan tunggal yang tepat mendapati pelbagai aplikasi.Denyutan ini kadang -kadang beroperasi tanpa penyegerakan ke kitaran jam, yang hanya dibenarkan apabila ketepatan sepenuhnya diabaikan.Walau bagaimanapun, sesetengah aplikasi memerlukan denyutan untuk menyelaraskan dengan sempurna lebar dan fasa dengan kitaran jam, yang memerlukan penggunaan penjana nadi tunggal yang diketengahkan.Penjana ini, diaktifkan oleh akhbar utama, bertujuan untuk menghasilkan denyutan yang konsisten, menyampaikan cabaran yang unik, terutama pengaruh jitter yang disebabkan oleh jam pada papan FPGA.

Cabaran penyegerakan

Pulsa pencetus manual, yang dipengaruhi oleh pembolehubah seperti jitter kerana sifat masa yang tidak dapat diramalkan dari masa akhbar utama, sering menghadapi cabaran teknikal.Penyelesaian pragmatik adalah penggunaan litar debounce, yang direka dengan rumit untuk menjinakkan input utama yang huru -hara.Litar ini dengan cekap menapis bunyi bising dan menstabilkan isyarat input, memupuk generasi nadi tunggal yang stabil.Dalam aplikasi dunia nyata, jurutera menarik kebijaksanaan dari pengalaman masa lalu, mendedahkan bahawa menggabungkan litar ini dengan ketara meningkatkan kebolehpercayaan sistem.

Mengatasi jitter yang disebabkan oleh jam

Jitter yang disebabkan oleh jam secara konsisten menimbulkan cabaran, berpotensi mengganggu masa nadi.Isu ini muncul dari ion V ariat dalam tempoh jam yang dapat mengubah masa yang penting untuk tugas -tugas tertentu.Pengurusan Jitter hasil daripada reka bentuk litar yang bijak dan penggunaan sumber FPGA yang berkesan.Finesse dalam meminimumkan jitter memastikan penjana nadi mengekalkan ketepatan yang diharapkan.Melalui ujian menyeluruh dan penentukuran yang tepat, pakar-pakar menyempurnakan sistem mereka, memastikan piawaian prestasi melepasi.

Merangkul Teknik Generasi Pulse Lanjutan

Mengejar generasi nadi yang sempurna memerlukan penggunaan metodologi yang canggih.Teknik seperti pengesanan kelebihan dan pengkondisian isyarat digunakan untuk menguatkan kesetiaan nadi.Pinjaman selanjutnya dari pendekatan kognitif, algoritma penyesuaian mungkin menstabilkan input secara halus.Pelaksanaan strategi canggih secara senyap -senyap mengoptimumkan prestasi sistem, mengelakkan perhatian yang tidak perlu.

Penjana Pulse Single dan Pulse Tunggal dalam Pembangunan FPGA

Membuat litar debounce

Merancang litar debounce utama yang berkesan untuk panggilan pintar kaunter.Kaunter ini penting untuk menapis bunyi yang mengganggu, menambat kestabilan dalam isyarat input.Saiz kaunter bergantung pada interaksi antara tempoh nadi jitter yang diharapkan dan kekerapan pensampelan jam.Untuk menampung tempoh jitter biasa, yang dikenal pasti dalam lingkungan 5 hingga 10 milisaat, seseorang mungkin mempertimbangkan modulus kaunter 20-bit yang berkesan dengan jam sistem 24 MHz.Matlamatnya adalah untuk menanamkan kelewatan hampir 22 milisaat, memastikan hanya isyarat konsistensi menavigasi, dengan itu mendaftarkan ketukan kekunci dengan tepat.Dalam operasi, apabila mengesan akhbar utama, kaunter memulakan dan, apabila memenuhi kiraannya, mengiktiraf isyarat mantap, memudahkan penciptaan nadi yang selamat.

Prinsip litar penjana nadi tunggal terkawal

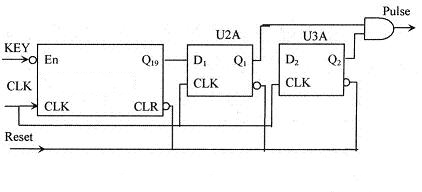

Penjana nadi tunggal yang dikawal utama menggunakan litar yang disebutkan di atas untuk menyelesaikan masalah utama dan mendapatkan isyarat yang stabil.Gunakan dua flop-flop dan pintu dan pintu untuk menghasilkan nadi tunggal, seperti yang ditunjukkan dalam Rajah 1.

D flip-flop U2A dicetuskan selepas menerima isyarat stabil d1 = 1.Terminal Q1 di flip-flop U2A mendapat nadi positif yang disegerakkan dengan CLK.Output Q1 hingga D Flip-Flop U3A, dapatkan nadi positif yang ditangguhkan oleh satu kitaran jam daripada Q1, dan terbalik output Q2 untuk mendapatkan nadi negatif.Output Q1 dan Qn2 sebagai input dan pintu akan mengeluarkan nadi tunggal dengan lebar nadi dua kali ganda dari kitaran jam asal.

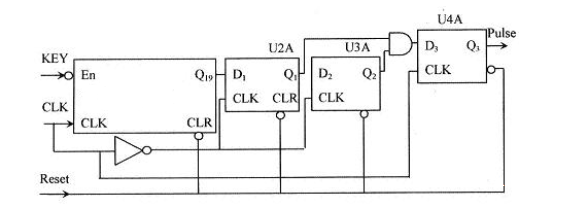

Untuk menjadikan lebar nadi nadi tunggal sama dengan tempoh jam dan fasa yang sama dengan tempoh jam, reka bentuk litar dalam Rajah 1 diperbaiki, seperti yang ditunjukkan dalam Rajah 2.

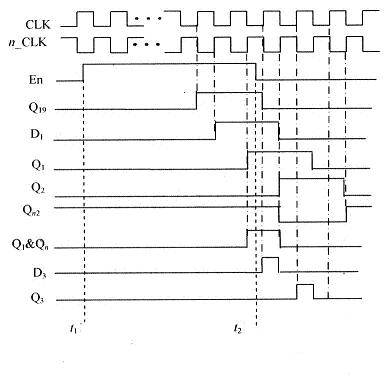

Dalam Rajah 2, pintu tidak ditambah sebelum jam dihantar ke flop d, supaya terminal Q1 menghasilkan nadi positif yang disegerakkan dengan NCLK (isyarat denyutan terbalik CLK), dan pintu keluar dari denyut nadi dan clk adalahPerbezaan kitaran setengah jam, kerana d input D4 dari flip-flop U4A dicetuskan di pinggir yang semakin meningkat CLK U4A, supaya lebar nadi denyutan tunggal adalah sama dengan kitaran jam, dan lebar nadi yang sama adalahsedar.Dan ditangguhkan oleh separuh kitaran jam untuk membuat nadi output sesuai dengan kitaran jam, untuk mencapai pelarasan fasa.Gambar rajah masa keseluruhan penjana nadi tunggal ditunjukkan dalam Rajah 3 (T1 dan T2 dalam Rajah 3 adalah momen apabila sebarang kekunci ditekan dan kunci dibangkitkan).

Keterangan Bahasa Verilog HDL Berdasarkan kaunter debounce utama dan penjana nadi tunggal di bawah FPGA

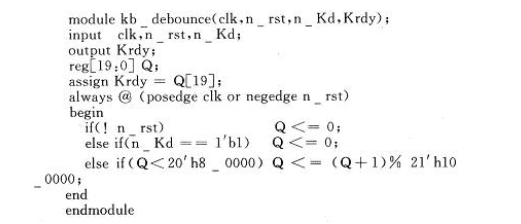

Litar kaunter debounce utama dalam Rajah 1, kod bahasa Verilog HDL untuk menggambarkan adalah seperti berikut:

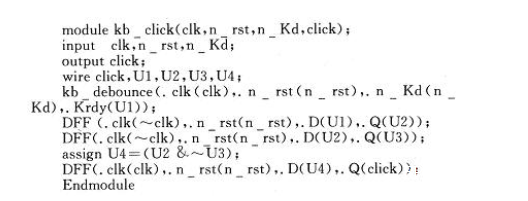

Reset N_RST dan Kunci N_KD dalam kod kedua -duanya rendah aktif.Kod bahasa Verilog HDL dari penjana nadi tunggal yang dikunci adalah seperti berikut:

DFF Flip-flop D juga digunakan dalam kod, kod untuk melaksanakan modul ini agak mudah

Kesimpulan

Reka bentuk ini berjaya memperkenalkan penjana nadi tunggal yang disegerakkan dengan kitaran jam, dengan teliti menyesuaikan diri dalam kedua -dua lebar nadi dan fasa untuk menangani cabaran debounce.Kebolehgunaannya membentangkan seluruh spektrum aplikasi FPGA yang luas, di mana output nadi tunggal yang tepat adalah permintaan.Litar debounce mempamerkan kesesuaian yang mengagumkan untuk memadankan konfigurasi FPGA yang pelbagai.Kaunter, yang dibuat untuk keperluan projek tertentu, mengintegrasikan pelarasan modulus untuk mengendalikan keadaan jitter yang berbeza -beza, dengan itu meningkatkan fleksibiliti dalam aplikasi.

TENTANG KITA

Kepuasan pelanggan setiap masa.Kepercayaan bersama dan kepentingan bersama.

TENTANG KITA

Kepuasan pelanggan setiap masa.Kepercayaan bersama dan kepentingan bersama.

ujian fungsi.Produk kos efektif tertinggi dan perkhidmatan terbaik adalah komitmen kekal kami.

Artikel panas

- LM358 Panduan Komprehensif Penguat Operasi Dual: Pinouts, Gambar Rajah Litar, Setara, Contoh Berguna

- Adakah CR2032 dan CR2016 boleh ditukar ganti?

- Memahami Perbezaan Analisis Teknikal dan Prestasi ESP32 dan ESP32-S3

- Memilih bateri yang betul: Panduan untuk AG4, LR626, LR66, 177/376/377, SR626, dan SR626SW setara

- Asas Transistor BC547: Pinout, Litar Aplikasi, Model Alternatif/Pelengkap

- NPN vs PNP: Apa perbezaannya?

- ESP32 vs STM32: Mikrokontroler mana yang lebih baik untuk anda?

- Apakah MOSFET dan bagaimana ia berfungsi?

- Asas Relay Elektrik: Operasi, Jenis dan Kegunaan Kerja

- Transistor PNP: Struktur, Prinsip Kerja dan Aplikasi

Memahami evolusi peranti yang boleh diprogramkan: Dari PAL ke FPGA

Memahami evolusi peranti yang boleh diprogramkan: Dari PAL ke FPGA

2024-12-17

SKM800GA176D Semikron PDF datasheet, simbol, pembungkusan

SKM800GA176D Semikron PDF datasheet, simbol, pembungkusan

2024-12-17

Nombor bahagian panas

C3225X7R2J683M200AA

C3225X7R2J683M200AA 08051A470FAT2A

08051A470FAT2A GRM216R71H183KA01D

GRM216R71H183KA01D CC0603KRX7R9BB101

CC0603KRX7R9BB101 06035A800JAT2A

06035A800JAT2A CC1206KKX7RABB273

CC1206KKX7RABB273 06031A1R8BAT4A

06031A1R8BAT4A GRM0335C1H2R0CD01D

GRM0335C1H2R0CD01D TAJC685M016RNJ

TAJC685M016RNJ DF13-4S-1.25C

DF13-4S-1.25C

- ICE65L04F-TCS63I

- CY7C1413KV18-300BZXC

- MAX359CWE+T

- TSI564A-10GCLY

- LC4256V-5TN144I

- LPC47N227-MV

- EP20K100FC324-1

- SKM50GB12T4

- XCV600E-6FG676I

- XR16C850IJTR-F

- SCANSTA111SMX

- PCM1808PW

- AD842JNZ

- XC6VSX315T-1FF1156I

- TL1451ACNSR

- LT1932ES6#TRMPBF

- BAS16LT1G

- LTC4308CMS8#PBF

- T491C107K010AT40537280

- 218S4PASA13G

- ACPL-P314V

- AK4520AVF-E2

- E28F016S3-120

- LFEC3E-4QN208C-3I

- LTC2444CG

- MT46H64M32LFCM-5IT:A

- R8A66175FP

- SA8500V1.1

- ST92F120V1Q7D/TR

- F432534PGE

- PI3B3126

- RTR8605-0-196NSP

- TCC8600-00X-EAR-AG

- 6MB175U4B-120-50

- TC9318AFAG-103

- LCMX0640C-3NT144C

- L9887-ICJP-JPZ1

- VI-910149

- IHLP1616BZER1R0MA1